English

English Deutsch

Deutsch| M I S T E R |

STRONA GŁÓWNA STRONA GŁÓWNA O FIRMIE O FIRMIE PRODUKTY PRODUKTY NOWOŚCI NOWOŚCI APLIKACJE PC APLIKACJE PC MONTAŻ SMD/THT MONTAŻ SMD/THT OBWODY DRUKOWANE OBWODY DRUKOWANE LISTA REFERENCYJNA LISTA REFERENCYJNA NASZE PUBLIKACJE NASZE PUBLIKACJE KONTAKT KONTAKT DOWNLOAD DOWNLOAD SKLEP SKLEP GALERIA GALERIA |

Tel. 608421274

Projektowanie FPGA w Altium Designer

Alpha

Altium Innovation Station zintegrowane środowisko składające się z oprogramowania Altium Designer i płyty uruchomieniowej NanoBoard - zapewnia komplet narzędzi i technologii potrzebnych do projektowania, implementacji, testowania i uruchamiania projektów FPGA, w czasie rzeczywistym. Dzięki tej zunifikowanej technologii możesz zarządzać całym projektem Altium bez zbytniego rozdrabniania się na szczegółach, dzięki czemu możesz skupić się na inteligencji i funkcjonalności urządzenia - Twoich produktów. Przed wyruszeniem w świat projektowania sprzętu, układów mikroprocesorowych i oprogramowania wbudowanego, jest wskazane solidne zrozumienie podstaw projektowania w tym innowacyjnym środowisku - jak implementować podstawowe elementy logiczne a następnie testowanie ich działania w rzeczywistym środowisku jaką może być płyta uruchomieniowa NanoBoard.

W tym artykule pokażemy implementację prostego układu logicznego opartego na podstawowych elementach logicznych FPGA jakimi są bramki, rejestry itp. (W kolejnych publikacjach pokażemy bardziej zaawansowane projekty z wykorzystaniem software-owych mikroprocesorów). W przykładowym projekcie zaimplementowano prosty licznik rewersyjny, który po zaprogramowaniu FPGA w płycie NanoBoard, spowoduje, że diody LED umieszczone na płycie będą zapalać się kolejno od lewej do prawej lub od prawej do lewej. W trakcie tego artykułu wskażemy jak korzystać z unifikowanego środowiska Altium Designer, płyty NanoBoard, wskażemy metodologię projektowania układów FPGA ze szczególnym uwzględnieniem: * Tworzenia projektu FPGA w środowisku Altium Designer czyli rysowanie schematu z wykorzystaniem z bibliotek podstawowych elementów logicznych.

* Uruchomienie projektu na płycie NanoBoard przy użyciu funkcji automatycznej konfiguracji.

* Przetwarzania projektu - kompilacji, syntezy i implementacji projektu, aby uzyskać plik wynikowe, które są używane do programowania urządzenia docelowego.

* Przykładowego projektu hierarchicznego FPGA, włączając w to przykład użycia prostej logiki w języku opisu sprzętu (HDL).

* Użycie narzędzi wspomagających programowanie.

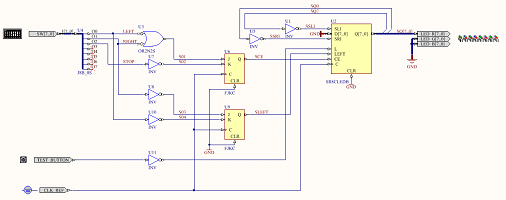

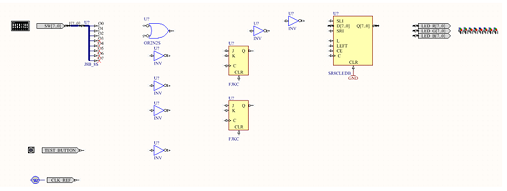

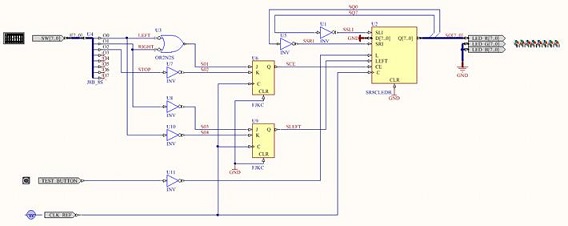

Schemat prostego licznika pierścieniowego pokazano na rys. 1.

Zanegowany najstarszy bit wyjściowy podłączony jest do wejścia SLI natomiast zanegowany najmłodszy bit wyjściowy podłączony jest do wejścia SRI. Zamiast budować taki licznik pierścieniowy z przerzutników D zastosujemy gotowy komponent rejestru przesuwnego SR8CLEDB. Biblioteki takich i podobnych komponentów znajdują się w pakiecie Altium.

Rys 1. Prosty licznik rewersyjny.

Sygnału zegarowy potrzebny do taktowania elementów logicznych w naszym układzie pobierany jest z płyty NanoBoard. Sygnały wyjściowe licznika podłączymy do diod świecących LED użytkownika wspomnianej płyty NB. Dodatkowa logika potrzebna w naszym projekcie do sterowania działaniem układu:

* KIERUNEK - Sposób przesuwania zawartości licznika: od lewej do prawej albo od prawej do lewej, w zależności od ustawienia przełącznika SW0 na płycie NanoBoard (część przełącznika DIP).

* STOP/START Licznik może być w trybie zatrzymany lub w trybie liczący, w zależności od ustawienia przełącznika na płycie NanoBoard (część przełącznika DIP).

* KASOWANIE Wyjście licznika można skasować (wszystkie LED wyłączone), przez naciśnięcie klawisza 'DAUGHTER BD TEST/RESET' na płycie NanoBoard.

Oprogramowanie narzędziowe

Zanim rozpoczniemy naszą przygodę z układami programowalnymi, należy zainstalować odpowiednie narzędzia producentów FPGA. Narzędzia te służą do wykonania syntezy i implementacji dla docelowego układu programowalnego. Narzędzia te nie są dostarczane z pakietem Altium Designer i powinny być pozyskane i zainstalowane niezależnie Więcej informacji na ten temat można znaleźć na stronach producenta:

* Actel Designeror Libero IDE www.actel.com. Oprogramowanie wymaga licencji. Sprawdź na www możliwe rodzaje licencji.

* Altera Quartus II from www.altera.com. Altera Quartus II Web Edition Oprogramowanie jest darmowe I nie wymaga licencji

* Lattice Diamond and ispLever from www.latticesemi.com. Oprogramowanie Diamond i ispLever Starter wymaga licencji. Sprawdź na www możliwe rodzaje licencji.

* Xilinx ISE from www.xilinx.com. ISE WebPACK oprogramowanie jest darmowe i nie wymaga licencji.

Ogólnie zasada jest taka że najnowsza wersja Altium Designer-a wspiera najnowsze oprogramowanie narzędziowe Xilinx i Altery.

Projekt

Pierwszą rzeczą, którą należy zrobić to przenieść koncepcję projektu do środowiska Altium Designer. Dla naszego prostego obwodu, będzie to oznaczać położenie niezbędnych elementów na schemacie i odpowiednie ich połączenie. Zanim będziemy mogli zająć się rysowaniem schematu najpierw jednak musimy stworzyć projekt. Kolejne punkty pokażą krok po kroku kolejne czynności przy tworzeniu projektu licznika pierścieniowego.

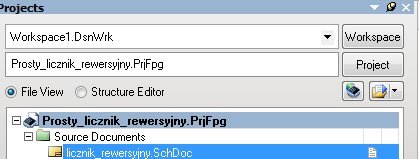

Projekt FPGA

Podstawą każdego projektu stworzonego w środowisku Altium Designer jest plik projektu. Dla projektu FPGA, musimy stworzyć nowy projekt FPGA (*. PrjFpg). Plik projektu jest plikiem ASCII, w którym zapisane są informacje o projekcie, takie jak dokumenty należące do projektu, ustawienia parametrów wyjściowych, ustawienia kompilacji, sposoby kontroli błędów, i tak dalej. Aby utworzyć projekt FPGA należy:

* Stworzyć nowy projekt FPGA poprzez wybranie: File New Project FPGA Project.

* Klikając prawym klawiszem na nazwie domyślnej projektu(Prosty_licznik_rewersyjny.PrjFpg) w panelu Projects należy zapisać projekt Save Project . Uwaga: Spacje i / lub myślnik (-), nie mogą być używane w projekcie lub w nazwach plików dokumentów. Może to spowodować błędy podczas syntezy. W zamian powinny być stosowane podkreślenia (_), w celu zapewnienia czytelności. Dodajemy pliki źródłowe do projektu

Projekt FPGA jest z natury projektem hierarchicznym. Dowolna liczba arkuszy schematu, dokumentów HDL (VHDL lub Verilog) lub dokumentów OpenBus może być dołączona do projektu w sposób hierarchiczny. Ale należy pamiętać, że dokument projektu nadrzędny tak zwany TOP LEVEL powinien być w postaci arkusza schematu. Arkusz ten zawiera nie tylko porty wejścia/wyjścia tzn. interfejs łączący piny fizycznego układu FPGA z portami projektu, ale również ułatwia integrację FPGA-PCB. W dalszej części artykułu pokażemy jak zbudować projekt hierarchiczny teraz będziemy pracować na jednym arkuszu (TOP LEVEL):

* Dodaj nowy arkusz schematu klikając prawym klawiszem na nazwie projektu w panelu Projects i wybierz Add New to Project Schematic. * Zapisz ten dokument (File Save) z nazwą licznik_rewersyjny.SchDoc, w tym samym folderze w którym znajduje się projekt.

* Powyższe działanie jest modyfikacją projektu, więc konieczne jest również zapisanie całego projektu. Zapisz projekt również (kliknij prawym przyciskiem myszy na jego nazwie i wybierz opcję Save Project).

Rys 2. Nowy projekt FPGA z jednym arkuszem schematu.

Rozmieszczenie elementów

Mamy pusty arkusz schematu nadszedł więc czas, aby dodać wymagane elementy, tak aby uzyskać zakładaną funkcjonalność projektu; elementy będziemy pobierać z bibliotek środowiska Altium Designer.

Tabela 1 pokazuje element potrzebne do budowy naszego licznika pierścieniowego. Wszystkie te elementy można pobrać z biblioteki FPGA Generic(FPGA Generic.IntLib), znajdującej się w folderze \Library\Fpga.

Tabela 1.Eelementy potrzebne do naszego projektu.

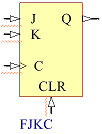

FJKC

FJKCPrzerzutnik J-K z asynchronicznym resetem

2 szt.

INV

INVNegator

6 szt.

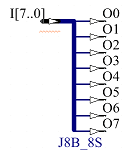

J8B_8S

J8B_8SŁącznik magistralowy magistrala ośmio bitowa na osiem pojedyńczych sygnałów.

1 szt.

OR2N2S

OR2N2S2-wejściowa bramka OR z zanegowanymi wejściami, (wersja z pojedynczymi wejściami)

1 szt.

SR8CLED

SR8CLED8-bitowy szeregowo równoległy rejestr przesuwny z wejściem ustawiającym, z maskowaniem zegara i asynchronicznym resetem(wersja z wyjściem magistralowym)

1 szt.

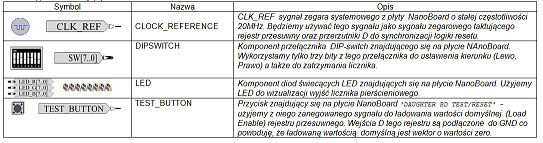

Tabela 2 określa elementy interfejsu naszego projektu.

Elementy te, powszechnie określane jako porty, łączą one sygnały ze schematu TOP LEVEL z rzeczywistymi pinami IO układu FPGA. Porty interfejsu znajdują się w bibliotece użytej płyty, w naszym przypadku FPGA NB3000 (FPGA NB3000 Port-Plugin.IntLib), również znajdującej się w folderze \Library\Fpga.

Tabela 2. Porty potrzebne do naszego projektu.

Symbol Nazwa Opis

CLOCK_REFERENCE

CLK_REF sygnał zegara systemowego z płyty NanoBoard o stałej częstotliwości 20MHz. Będziemy używać tego sygnału jako sygnału zegarowego taktującego rejestr przesuwny oraz przerzutniki D do synchronizacji logiki resetu.

DIPSWITCH

Komponent przełącznika DIP-switch znajdującego się na płycie NAnoBoard. Wykorzystamy tylko trzy bity z tego przełącznika do ustawienia kierunku (Lewo, Prawo) a także do zatrzymania licznika.

LED

Komponent diod świecących LED znajdujących się na płycie NanoBoard. Użyjemy LED do wizualizacji wyjść licznika pierścieniowego.

TEST_BUTTON

Przycisk znajdujący się na płycie NanoBoard "DAUGHTER BD TEST RESET" - użyjemy z niego zanegowanego sygnału do ładowania wartości domyślnej (Load Enable) rejestru przesuwnego. Wejścia D tego rejestru są podłączone do GND co powoduję, że ładowaną wartością domyślną jest wektor o wartości zero.

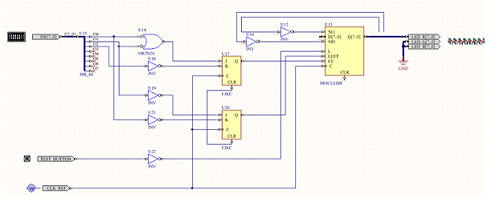

Na arkuszu schematu rozmieść elementy jak na rysunku 3. Elementy znajdują się w bibliotekach zintegrowanych które są instalowane domyślnie z pakietem Altium Designer. Biblioteki są dostępne w panelu Libraries. Z tym panelu należy otworzyć odpowiednią bibliotekę i wybrać odpowiedni element klikając Place. Za pomocą spacji można elementy obracać w zależności od potrzeb. Po rozmieszczeniu elementów na arkuszu należy je ponumerować. Najszybciej to można zrobić wybierając polecenie Tools Annotate Schematics Quietly .

Rys 3 Wstępne rozmieszczenie elementów na arkuszu schematu.

Połączenia

Elementy znajdujące się na arkuszu schematu należy w odpowiedni sposób połączyć.

* Aby połączyć elementy wybierz polecenia z menu Place Wire lub Place Bus .

Rys 4. Widok połączeń projektu.

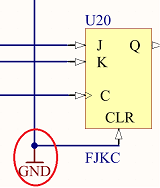

* Z paska narzędziowego wybierz ikonkę GND aby umieścić symbol GND. Zanim symbol położysz na schemacie możesz go edytować klikając klawisz Tab. W oknie dialogowym możesz zmienić m. in Style wybierając np. opcję Bar. Teraz połóż symbol GND łącząc go z wejściem CLR rejestru D.

Rys 5. Przerzutnik - połączenie GND.

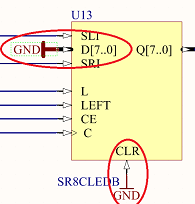

* Kolejny symbol GND połącz do wejścia CLR rejestru przesuwnego.

* Z paska narzędziowego Wiring, wybierz ikonkę

jako symbol magistrali GND. Podobnie jak poprzednio zmień Style na Bar. Następnie wstaw ten symbol na schemacie w miejscu D[7..0] rejestru przesuwnego. Klawiszem spacji możesz obrócić symbol jeżeli to jest konieczne.

jako symbol magistrali GND. Podobnie jak poprzednio zmień Style na Bar. Następnie wstaw ten symbol na schemacie w miejscu D[7..0] rejestru przesuwnego. Klawiszem spacji możesz obrócić symbol jeżeli to jest konieczne.

Rys. 6. Rejestr przesuwny połączenie GND.

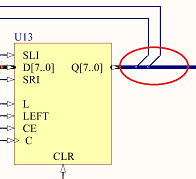

* Kolejnym krokiem jest dodanie dwóch indywidualnych wyjść magistralowych z magistrali dołączonej do wyjścia rejestru przesuwnego. Te wyjścia są potrzebne do zrobienia odpowiedniego sprzężenia zwrotnego. Zanegowane zostaną podłączone odpowiednio do wejść SLI I SRI rejestru przesuwnego jak to pokazano na rysunku 7.

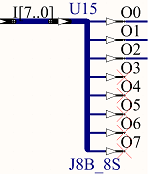

Rys. 7. Dodanie wyjść magistralowych.

* W celu uporządkowania projektu i zminimalizowania ilości ostrzeżeń po komunikacji możemy wstawić na arkuszu schematu dyrektywy No ERC na każdym nie połączonym wyjściu rozcięcia magistralowego (U15). Z belki narzędziowej Wiring, wybierz ikonkę No ERC i umieść na schemacie. Dyrektywę No ERC należy umieścić na każdym nie podłączonym wyjściu O3 to O7, jak pokazano na rysunku 7.

Rys. 8. Dyrektywy No ERC.

Aby zakończyć nasz projekt, musimy dodać jeszcze etykiety magistrali do naszego obwodu. Dzięki temu projekt będzie łatwiejszy do zrozumienia a także będzie łatwiejszy do uruchomienia. * Aby dodać etykiety jak na rysunku 9, użyj Place Net Label.

Rys 9. Kompletny projekt ze wszystkimi etykietami i połączeniami..

* Na zakończenie zapisz cały projekt (File Save All).

W kolejnej części pokażemy jak przeprowadzić syntezę, implementację naszego projektu.

Wojciech Pietrasina

mister@mister.net.pl

Aktualizacja 2021