English

English Deutsch

Deutsch| M I S T E R |

STRONA GŁÓWNA STRONA GŁÓWNA O FIRMIE O FIRMIE PRODUKTY PRODUKTY NOWOŚCI NOWOŚCI APLIKACJE PC APLIKACJE PC MONTAŻ SMD/THT MONTAŻ SMD/THT OBWODY DRUKOWANE OBWODY DRUKOWANE LISTA REFERENCYJNA LISTA REFERENCYJNA NASZE PUBLIKACJE NASZE PUBLIKACJE KONTAKT KONTAKT DOWNLOAD DOWNLOAD SKLEP SKLEP GALERIA GALERIA |

Tel. 608421274

Weryfikacja projektu.

W poprzednim odcinku zaprojektowaliśmy projekt prostego licznika rewersyjnego, obecnie zrobimy weryfikację a następnie konfigurację projektu.

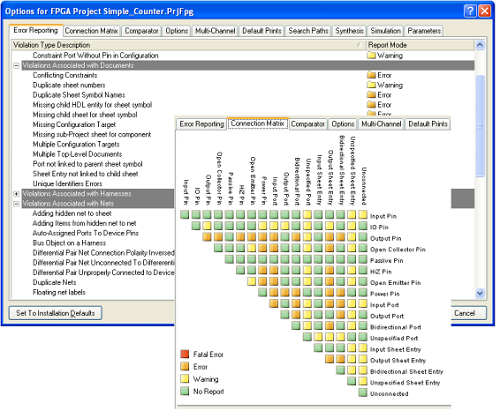

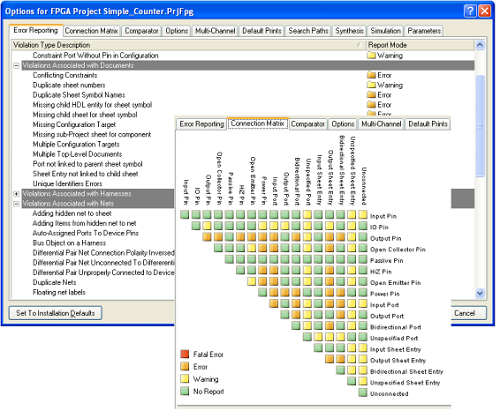

Zanim zaczniemy syntezę i implementację naszego projektu powinniśmy wykonać jego weryfikację. Altium Designer daje nam do tego zaawansowane narzędzie. W środowisku Altium Designer proces kompilacji jest integralną częścią tworzenia net listy - pliku w którym zawarte są m. in. informacje na temat wzajemnych połączeń modułów. W trakcie tego procesu sprawdzany jest zakres połączeń elektrycznych oraz błędy schematu zgodnie z opcjami zdefiniowanymi w zakładkach Error Reporting oraz Connection Matrix z okna Options for FPGA Project (Project " Project Options).

Rysunek 1. Ustawienia kompilatora. Zakładki Error Reporting i Connection Matrix.

Uwaga: Dla tego projektu ustawienia domyślne są poprawne i nie wymagają modyfikacji.

" Mając otwarty schemat należy wybrać Project " Compile FPGA Project Simple_Counter.PrjFpg. Zostanie uruchomiony proces kompilacji projektu.

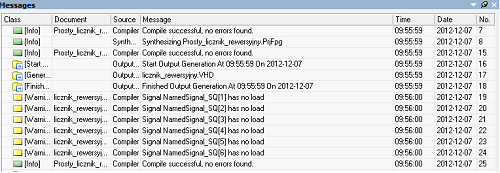

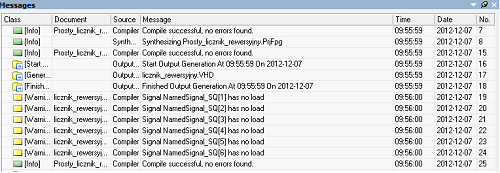

" Wszelkie Ostrzeżenia (Warnings), błędy (Errors) oraz błędy krytyczne (Fatal Errors) zostaną wyświetlone na panelu Messages. Jeżeli pojawią się w projekcie podczas kompilacji jakieś błędy lub błędy krytyczne okno Messages zostanie wyświetlone automatycznie. Jeżeli są tylko ostrzeżenia, możesz otworzyć ten panel ręcznie - klikając zakładkę System znajdującą się na pasku statusu Status Bar w prawym dolnym rogu pod arkuszem edytora schematu, następnie wybierając okno Messages. Podwójne kliknięcie na wiadomości (ostrzeżeniu lub błędzie) wyświetli szczegółowe informację odnośnie tego komunikatu na panelu Compile Errors. Jednocześnie miejsce potencjalnego problemu zostanie na schemacie powiększone i zaznaczone.

" Na naszym schemacie (licznik_rewersyjny.SchDoc) połączenia są poprawne, zwróć uwagę na kilka ostrzeżeń które widnieją w panelu Messages - informują one o braku podłączeń wyjść magistrali SQ[7..0]. Dzieje się tak dlatego, że z magistrali SQ wykorzystujemy linię SQ0 pozostałe linie SQ1 do SQ7 są nie podłączone w tym projekcie.

Rysunek 2. Okno z komunikatami po kompilacji.

Jeżeli w panelu Messages widzisz komunikat o błędzie musisz zlokalizować miejsce występowania problemu, poprawić schemat i skompilować projekt ponownie.

" Zapisz pliki schematu oraz cały projekt.

Konfiguracja Projektu

Kolejnym etapem będzie określenie w jakim układzie FPGA mamy zamiar zaimplementować nasz projekt aby ostatecznie móc sprawdzić jego działanie. W naszym przykładzie wybierzemy płytę dostarczaną przez Altium Designer - NanoBoard 3000 z układem FPGA XC3S1400AN.

Proces mapowania czyli powiązania portów układu FPGA ze światem zewnętrznym odbywa się za pośrednictwem tak zwanych plików ograniczeń. Pliki te zawierają minimum informacji o projekcie, pozwalające na jego syntezę i implementację. Takimi podstawowymi informacjami są: specyfikacja układu FPGA, mapowanie portów do fizycznych wyprowadzeń układu FPGA, definicja standard IO, ograniczenia związane z wartością częstotliwości zegarowych , zależności czasowych.

Zestaw jednego lub więcej plików ograniczeń w zależności od złożoności projektu składa się na konfigurację projektu - innymi słowy konfiguracją projektu nazywamy listę plików ograniczeń wchodzących w skład tego projektu.

W odniesieniu do uniwersalnej płyty uruchomieniowej możemy podzielić pliki ograniczeń na:

" Określające połączenia - mapowanie pinów odnoszące się do danej płyty bazowej jak i wchodzącej w jej skład różnego rodzaju adapterów, przejściówek( połączenia pomiędzy FPGA czy innymi układami peryferyjnymi, a ich złączami połączeniowymi).

" Określające połączenia pomiędzy płytą bazową a wchodzącymi w jej skład różnego rodzaju adapterów, przejściówek (połączenia złącze - złącze). Projekt FPGA uruchamiany na płycie NanoBoard można skonfigurować ręcznie przez dodanie odpowiednich plików konfiguracyjnych lecz środowisko Altium Designer dostarcza nam narzędzia do automatycznej konfiguracji projektu.

Kluczem do wykonania auto-konfiguracji projektu jest zdolność systemu do automatycznej identyfikacji zasobów sprzętowych. Identyfikacja jest możliwa dzięki umieszczeniu na płycie i na wszystkich pozostałych modułach układów scalonych tzw. "elektronicznych numerów seryjnych" połączonych magistralą 1-Wire.

Użycie tej cechy pozwoli na wykonanie konfiguracji automatycznie. Potrzebne pliki ograniczeń są automatycznie wybierane i dodawane do konfiguracji w zależności od tego jaki sprzęt został zidentyfikowany(płyta bazowa , adaptery).

Uwaga: Starsze adaptery posiadające dwa złącza mogą być co prawda użyte w płytach NanoBoard (np. na NB2DSK01), lecz nie jest możliwe ich wykrycie w procesie auto konfiguracji gdyż nie posiadają układów identyfikacyjnych.

Przejdźmy do konfiguracji naszego projektu.

" Przed rozpoczęciem korzystania z funkcji automatycznej konfiguracji, upewnij się, że płyta NanoBoard jest podpięta do komputera za pomocą magistrali USB.

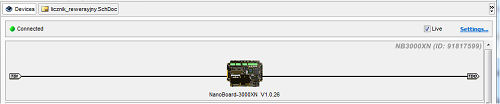

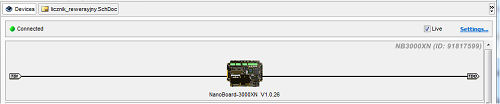

" Otwórz widok urządzeń Devices (View " Devices View). Zaznacz opcję Live i poczekaj, aż wskaźnik Connected zmieni kolor na zielony.

Rysunek 3. Widok poprawnie rozpoznanej płyty NanoBoard przez środowisko Altium..

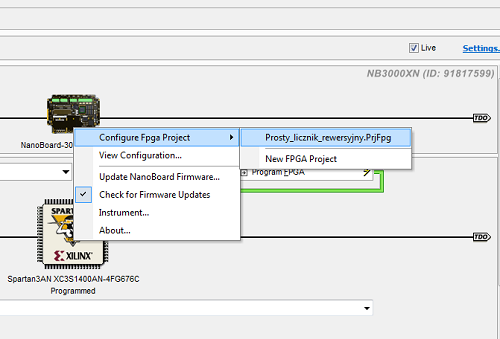

" Proces auto-konfiguracji można przeprowadzić na dwa sposoby. Na potrzeby tego artykułu pokażemy obie metody. Natomiast w rzeczywistości należy zrobić auto-konfigurację według jednej wybranej metody:

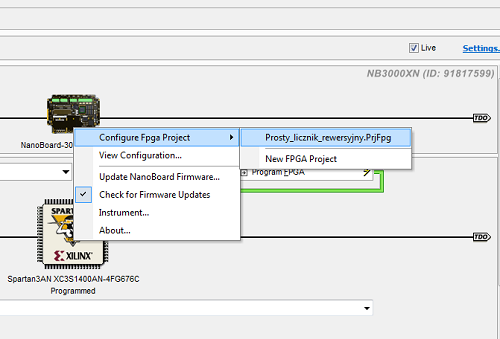

Metoda 1: Kliknij na płycie NanoBoard prawym klawiszem, z rozwijanej listy wybierz klawiszem Configure Fpga Project " Prosty_licznik_rewersyjny.PrjFpg (Rysunek 4).

Rysunek 4. Auto-konfiguracja z widoku urządzenia Devices.

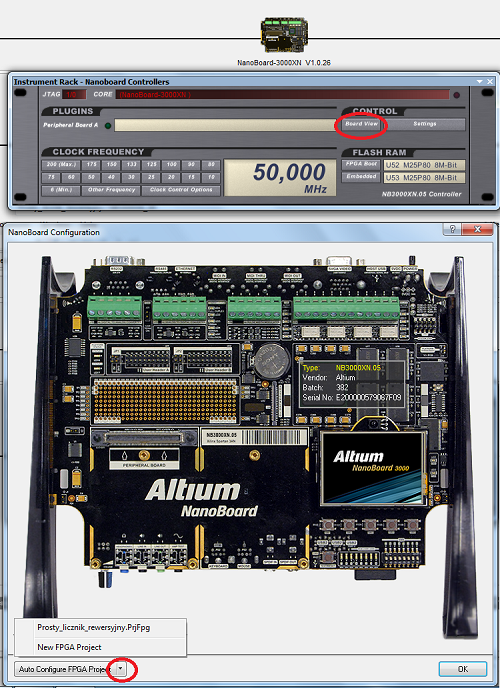

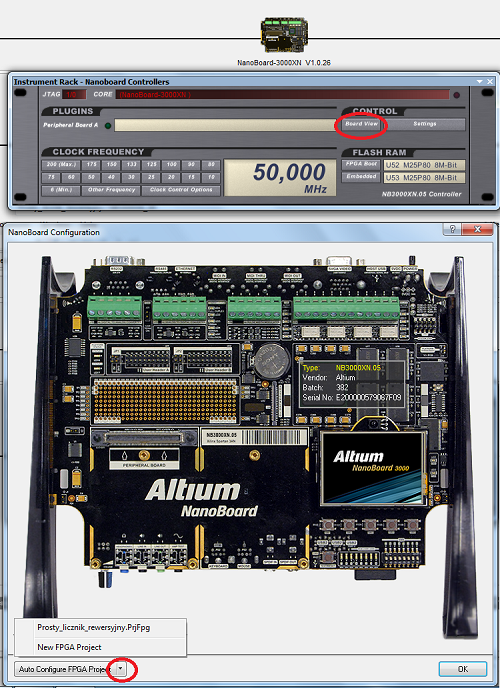

Metoda 2: Kliknij dwukrotnie na płycie NanoBoard aby otworzyć panel NanoBoard - narzędzie konfiguracyjne płytę NanoBoard. Następnie kliknij przycisk View button aby otworzyć okno dialogowe NanoBoard Configuration. Następnie rozwiń listę Auto Configure FPGA Project i wybierz Prosty_licznik_rewersyjny.PrjFpg (Rys 5).

Rysunek 5. Auto-konfiguracja z okna widoku płyty.

Proces auto-konfiguracji będzie postępował w kolejnych etapach:

" Zostanie otworzone okno menadżera konfiguracji dodany Prosty_licznik_rewersyjny. Określenie nazwy konfiguracji jest zależne od wersji Twojej płyty NanoBoard i ewentualnie użytych adapterów. Ogólnie na format nazwy konfiguracji składają się wersja płyty bazowej oraz wersja adaptera do niej dołączonego: motherboard code_revision_daughter board code_revision

Dla przykładu dla płyty NanoBoard NB2DSK01 (wersja 8), i adaptera Xilinx Spartan-3 oznaczenie DB30 (wersja 6), zostanie wygenerowana konfiguracja NB2DSK01_08_DB30_06. " Do konfiguracji zostaną dodane pliki ograniczeń - do płyty, i każdego z adapterów. Liki źródłowe znajdują się w katalogu \Library\Fpga\NB3000 Constraint Files. W każdym przypadku użyte pliki są zależne od użytego w projekcie sprzętu i jego wersji. Dla przykładu jeżeli w projekcie jest użyty Xilinx Spartan-3 oznaczenie DB30 (wersja 6), wtedy plik który zostanie pobrany i dodany do konfiguracji to DB30.06.Constraint.

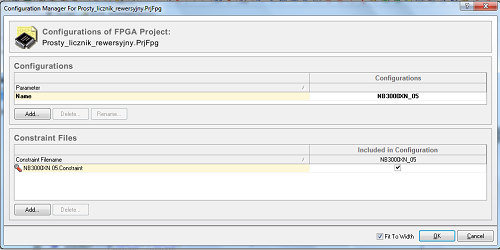

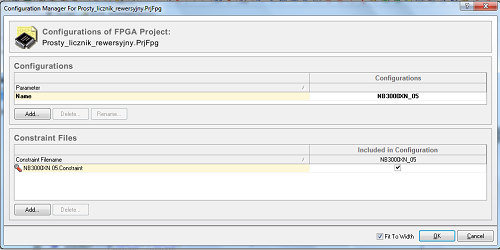

" Pliki ograniczeń definiujące połączenia między poszczególnymi modułami a płytą bazową są tworzone na " w locie" i dodawane do konfiguracji. Nazwa takich plików składa się z nazwy konfiguracji oraz dodatkowego sufiksu '_BoardMapping' (np. NB2DSK01_08_DB30_06_BoardMapping.Constraint). Pliki te zostaną zapisane w tej samej lokalizacji co plik projektu (Prosty_licznik_rewersyjny.PrjFpg). " Konfiguracja i przypisane do niej pliki widnieją w oknie menadżera konfiguracji ( Configuration Manager) jak pokazano na rysunku 6.

Rysunek 6. Menadżer konfiguracji dla projektu Prosty_licznik_rewersyjny.

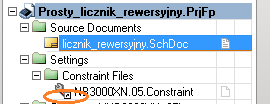

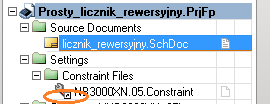

Kliknij OK. a katalog Settings zostanie dodany do projektu (rysunek 7), a następnie pojawi się na panelu Projects . Pliki ograniczeń zostaną wyświetlone w katalogu Constraint Files. Mała ikonka (zaznaczona na rysunku) wskazuje, że plik jest zlinkowany z projektem, czyli jego żródła znajdują się poza katalogiem projektu.

Rysunek 7. Pliki ograniczeń dodane do projektu.

" Zapisz plik projektu.

Na obecnym etapie mamy skonfigurowany projekt, kolejnym etapem będzie zrobienie syntezy a następnie implementacji.

Wojciech Pietrasina

W poprzednim odcinku zaprojektowaliśmy projekt prostego licznika rewersyjnego, obecnie zrobimy weryfikację a następnie konfigurację projektu.

Zanim zaczniemy syntezę i implementację naszego projektu powinniśmy wykonać jego weryfikację. Altium Designer daje nam do tego zaawansowane narzędzie. W środowisku Altium Designer proces kompilacji jest integralną częścią tworzenia net listy - pliku w którym zawarte są m. in. informacje na temat wzajemnych połączeń modułów. W trakcie tego procesu sprawdzany jest zakres połączeń elektrycznych oraz błędy schematu zgodnie z opcjami zdefiniowanymi w zakładkach Error Reporting oraz Connection Matrix z okna Options for FPGA Project (Project " Project Options).

Rysunek 1. Ustawienia kompilatora. Zakładki Error Reporting i Connection Matrix.

Uwaga: Dla tego projektu ustawienia domyślne są poprawne i nie wymagają modyfikacji.

" Mając otwarty schemat należy wybrać Project " Compile FPGA Project Simple_Counter.PrjFpg. Zostanie uruchomiony proces kompilacji projektu.

" Wszelkie Ostrzeżenia (Warnings), błędy (Errors) oraz błędy krytyczne (Fatal Errors) zostaną wyświetlone na panelu Messages. Jeżeli pojawią się w projekcie podczas kompilacji jakieś błędy lub błędy krytyczne okno Messages zostanie wyświetlone automatycznie. Jeżeli są tylko ostrzeżenia, możesz otworzyć ten panel ręcznie - klikając zakładkę System znajdującą się na pasku statusu Status Bar w prawym dolnym rogu pod arkuszem edytora schematu, następnie wybierając okno Messages. Podwójne kliknięcie na wiadomości (ostrzeżeniu lub błędzie) wyświetli szczegółowe informację odnośnie tego komunikatu na panelu Compile Errors. Jednocześnie miejsce potencjalnego problemu zostanie na schemacie powiększone i zaznaczone.

" Na naszym schemacie (licznik_rewersyjny.SchDoc) połączenia są poprawne, zwróć uwagę na kilka ostrzeżeń które widnieją w panelu Messages - informują one o braku podłączeń wyjść magistrali SQ[7..0]. Dzieje się tak dlatego, że z magistrali SQ wykorzystujemy linię SQ0 pozostałe linie SQ1 do SQ7 są nie podłączone w tym projekcie.

Rysunek 2. Okno z komunikatami po kompilacji.

Jeżeli w panelu Messages widzisz komunikat o błędzie musisz zlokalizować miejsce występowania problemu, poprawić schemat i skompilować projekt ponownie.

" Zapisz pliki schematu oraz cały projekt.

Konfiguracja Projektu

Kolejnym etapem będzie określenie w jakim układzie FPGA mamy zamiar zaimplementować nasz projekt aby ostatecznie móc sprawdzić jego działanie. W naszym przykładzie wybierzemy płytę dostarczaną przez Altium Designer - NanoBoard 3000 z układem FPGA XC3S1400AN.

Proces mapowania czyli powiązania portów układu FPGA ze światem zewnętrznym odbywa się za pośrednictwem tak zwanych plików ograniczeń. Pliki te zawierają minimum informacji o projekcie, pozwalające na jego syntezę i implementację. Takimi podstawowymi informacjami są: specyfikacja układu FPGA, mapowanie portów do fizycznych wyprowadzeń układu FPGA, definicja standard IO, ograniczenia związane z wartością częstotliwości zegarowych , zależności czasowych.

Zestaw jednego lub więcej plików ograniczeń w zależności od złożoności projektu składa się na konfigurację projektu - innymi słowy konfiguracją projektu nazywamy listę plików ograniczeń wchodzących w skład tego projektu.

W odniesieniu do uniwersalnej płyty uruchomieniowej możemy podzielić pliki ograniczeń na:

" Określające połączenia - mapowanie pinów odnoszące się do danej płyty bazowej jak i wchodzącej w jej skład różnego rodzaju adapterów, przejściówek( połączenia pomiędzy FPGA czy innymi układami peryferyjnymi, a ich złączami połączeniowymi).

" Określające połączenia pomiędzy płytą bazową a wchodzącymi w jej skład różnego rodzaju adapterów, przejściówek (połączenia złącze - złącze). Projekt FPGA uruchamiany na płycie NanoBoard można skonfigurować ręcznie przez dodanie odpowiednich plików konfiguracyjnych lecz środowisko Altium Designer dostarcza nam narzędzia do automatycznej konfiguracji projektu.

Kluczem do wykonania auto-konfiguracji projektu jest zdolność systemu do automatycznej identyfikacji zasobów sprzętowych. Identyfikacja jest możliwa dzięki umieszczeniu na płycie i na wszystkich pozostałych modułach układów scalonych tzw. "elektronicznych numerów seryjnych" połączonych magistralą 1-Wire.

Użycie tej cechy pozwoli na wykonanie konfiguracji automatycznie. Potrzebne pliki ograniczeń są automatycznie wybierane i dodawane do konfiguracji w zależności od tego jaki sprzęt został zidentyfikowany(płyta bazowa , adaptery).

Uwaga: Starsze adaptery posiadające dwa złącza mogą być co prawda użyte w płytach NanoBoard (np. na NB2DSK01), lecz nie jest możliwe ich wykrycie w procesie auto konfiguracji gdyż nie posiadają układów identyfikacyjnych.

Przejdźmy do konfiguracji naszego projektu.

" Przed rozpoczęciem korzystania z funkcji automatycznej konfiguracji, upewnij się, że płyta NanoBoard jest podpięta do komputera za pomocą magistrali USB.

" Otwórz widok urządzeń Devices (View " Devices View). Zaznacz opcję Live i poczekaj, aż wskaźnik Connected zmieni kolor na zielony.

Rysunek 3. Widok poprawnie rozpoznanej płyty NanoBoard przez środowisko Altium..

" Proces auto-konfiguracji można przeprowadzić na dwa sposoby. Na potrzeby tego artykułu pokażemy obie metody. Natomiast w rzeczywistości należy zrobić auto-konfigurację według jednej wybranej metody:

Metoda 1: Kliknij na płycie NanoBoard prawym klawiszem, z rozwijanej listy wybierz klawiszem Configure Fpga Project " Prosty_licznik_rewersyjny.PrjFpg (Rysunek 4).

Rysunek 4. Auto-konfiguracja z widoku urządzenia Devices.

Metoda 2: Kliknij dwukrotnie na płycie NanoBoard aby otworzyć panel NanoBoard - narzędzie konfiguracyjne płytę NanoBoard. Następnie kliknij przycisk View button aby otworzyć okno dialogowe NanoBoard Configuration. Następnie rozwiń listę Auto Configure FPGA Project i wybierz Prosty_licznik_rewersyjny.PrjFpg (Rys 5).

Rysunek 5. Auto-konfiguracja z okna widoku płyty.

Proces auto-konfiguracji będzie postępował w kolejnych etapach:

" Zostanie otworzone okno menadżera konfiguracji dodany Prosty_licznik_rewersyjny. Określenie nazwy konfiguracji jest zależne od wersji Twojej płyty NanoBoard i ewentualnie użytych adapterów. Ogólnie na format nazwy konfiguracji składają się wersja płyty bazowej oraz wersja adaptera do niej dołączonego: motherboard code_revision_daughter board code_revision

Dla przykładu dla płyty NanoBoard NB2DSK01 (wersja 8), i adaptera Xilinx Spartan-3 oznaczenie DB30 (wersja 6), zostanie wygenerowana konfiguracja NB2DSK01_08_DB30_06. " Do konfiguracji zostaną dodane pliki ograniczeń - do płyty, i każdego z adapterów. Liki źródłowe znajdują się w katalogu \Library\Fpga\NB3000 Constraint Files. W każdym przypadku użyte pliki są zależne od użytego w projekcie sprzętu i jego wersji. Dla przykładu jeżeli w projekcie jest użyty Xilinx Spartan-3 oznaczenie DB30 (wersja 6), wtedy plik który zostanie pobrany i dodany do konfiguracji to DB30.06.Constraint.

" Pliki ograniczeń definiujące połączenia między poszczególnymi modułami a płytą bazową są tworzone na " w locie" i dodawane do konfiguracji. Nazwa takich plików składa się z nazwy konfiguracji oraz dodatkowego sufiksu '_BoardMapping' (np. NB2DSK01_08_DB30_06_BoardMapping.Constraint). Pliki te zostaną zapisane w tej samej lokalizacji co plik projektu (Prosty_licznik_rewersyjny.PrjFpg). " Konfiguracja i przypisane do niej pliki widnieją w oknie menadżera konfiguracji ( Configuration Manager) jak pokazano na rysunku 6.

Rysunek 6. Menadżer konfiguracji dla projektu Prosty_licznik_rewersyjny.

Kliknij OK. a katalog Settings zostanie dodany do projektu (rysunek 7), a następnie pojawi się na panelu Projects . Pliki ograniczeń zostaną wyświetlone w katalogu Constraint Files. Mała ikonka (zaznaczona na rysunku) wskazuje, że plik jest zlinkowany z projektem, czyli jego żródła znajdują się poza katalogiem projektu.

Rysunek 7. Pliki ograniczeń dodane do projektu.

" Zapisz plik projektu.

Na obecnym etapie mamy skonfigurowany projekt, kolejnym etapem będzie zrobienie syntezy a następnie implementacji.

Wojciech Pietrasina

mister@mister.net.pl

Aktualizacja 2021